System On Chip Interfaces For Low Power Design Pdf

System on chip interfaces for low power design pdf. System on chip interfaces for low power design Feb 11 2021. Posted By Michael Crichton Library TEXT ID a4678ea5. Low cost Lowest possible area Technology behind the leading edge High level of integration of peripherals reduces system cost Fast time to market Compatible architectures eg.

Power consumption is an important element in designing a system particularly in todays battery powered world. In NoC the overall power dissipation is due to the interconnection system. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involvedThe book offers a common context to help understand the variety of available interfaces and make sense of technology from different vendors aligned with.

The processor may be a custom or standard microprocessor or it could be a specialised media processor for sound Easter Term 2011 2 System-On-Chip DM. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involved. PDF On Sep 9 2015 Jie Jin and others published Low Power Design for On-chip Networking Processing System Find read and cite all the research you need on ResearchGate.

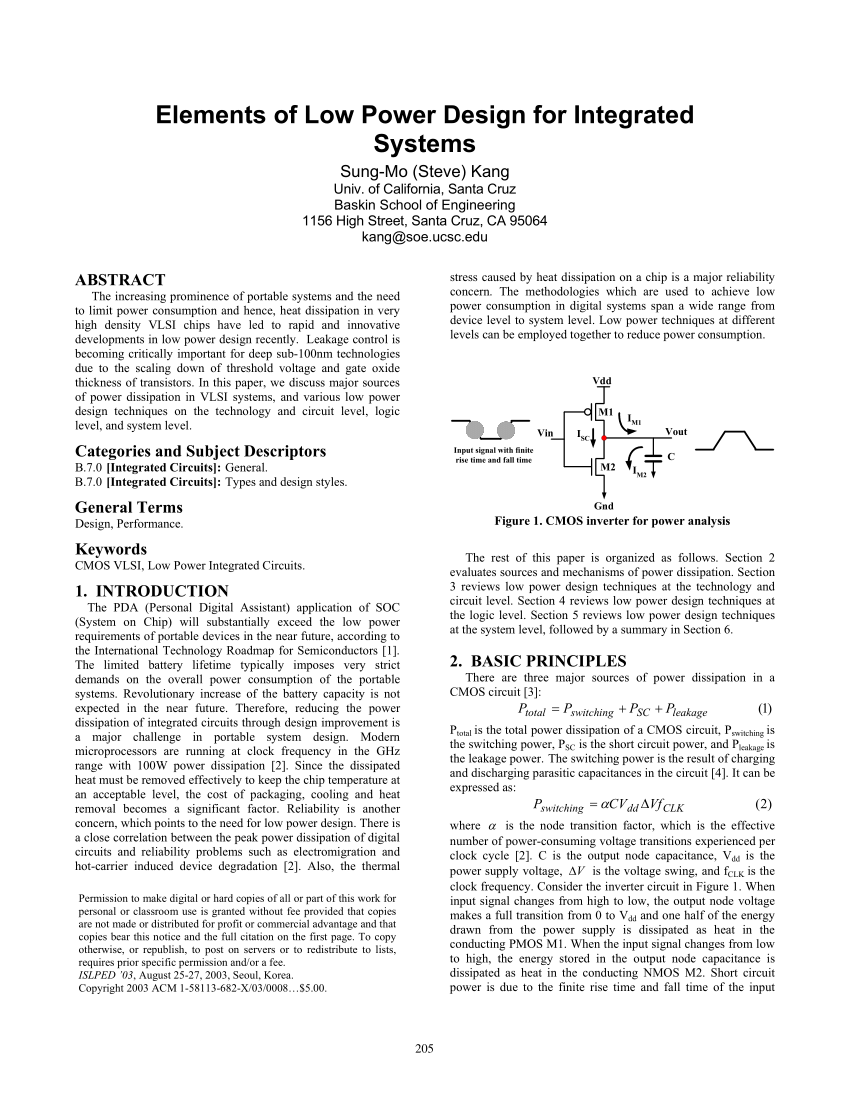

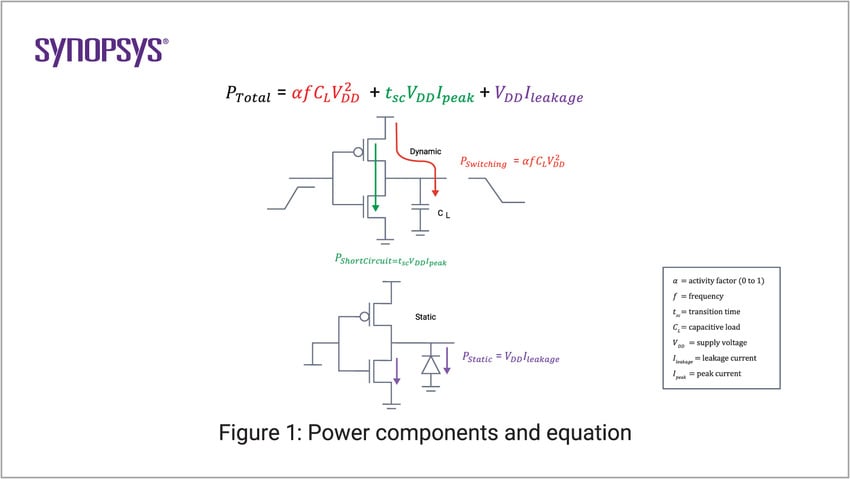

Describe all the interfaces between the design and its environment. Low Power System-on-Chip Design Advanced Power Modeling Support in todays EDA Flows Petri Solanti CAE Synopsys Finland Oy 1 Advanced Power Modeling Support in todays EDA Flows 2312009. The System-On-Chip Design Process 2.

System On Chip Interfaces For Low Power Design. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involvedThe book offers a common context to help understand the variety of available interfaces and make sense of technology from different vendors aligned with. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involved.

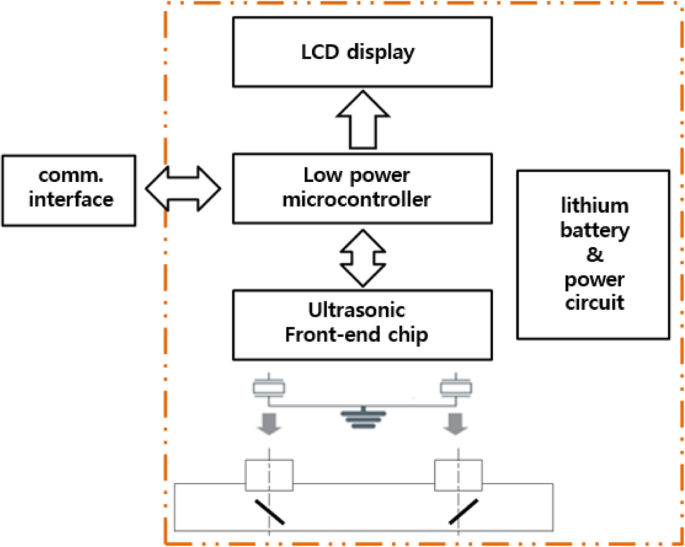

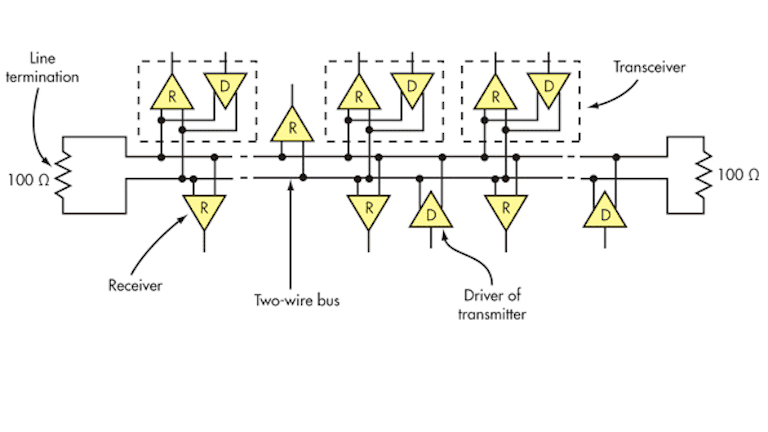

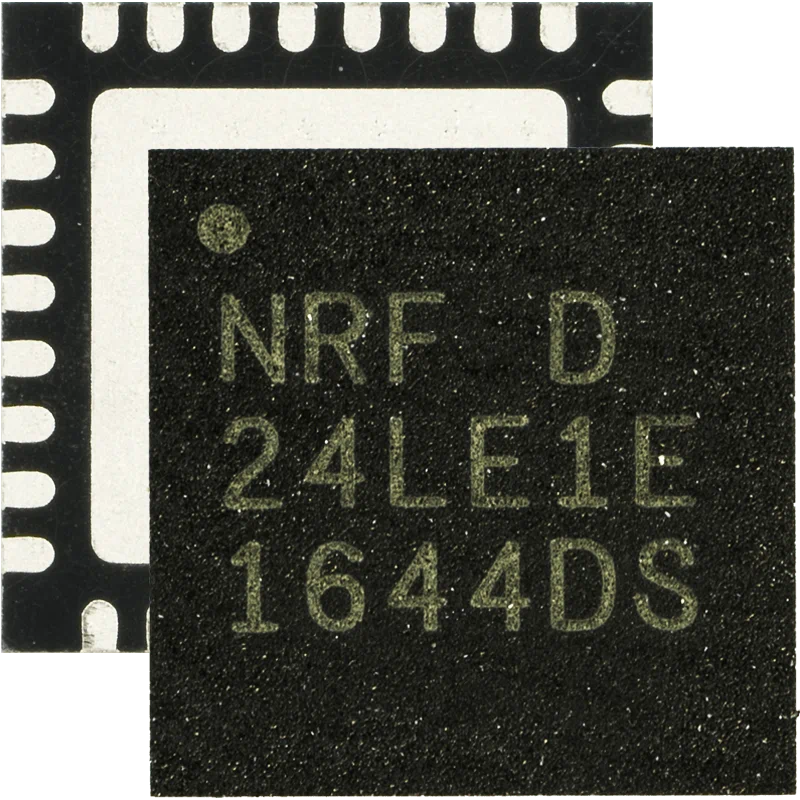

Now You Get PDF BOOK. The NCS36510 is a low power fully integrated System on Chip that integrates a 24 GHz IEEE 802154 compliant transceiver Arm CortexM3 microprocessor RAM and FLASH memory a true random number generator and multiple peripherals to support design of a complete and secure wireless network with minimal external components. HSIC USB signaling and operation.

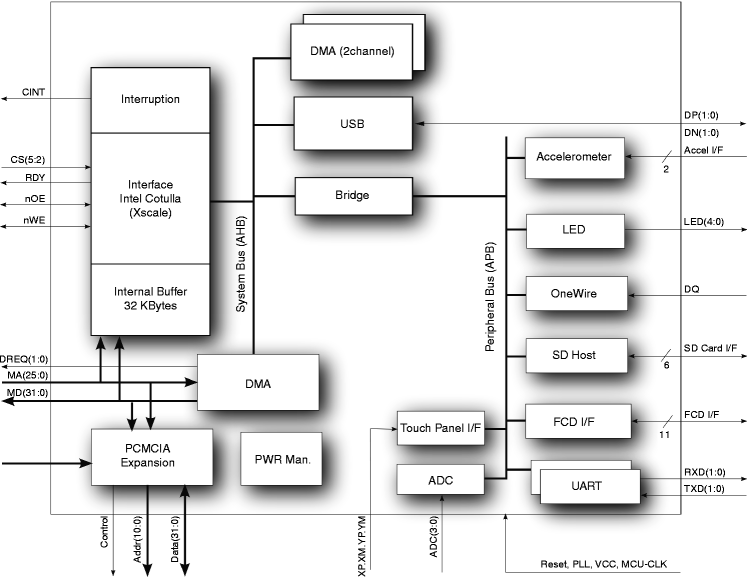

A system includes a microprocessor memory and peripherals. An HSIC interface is built on two signals.

System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involved.

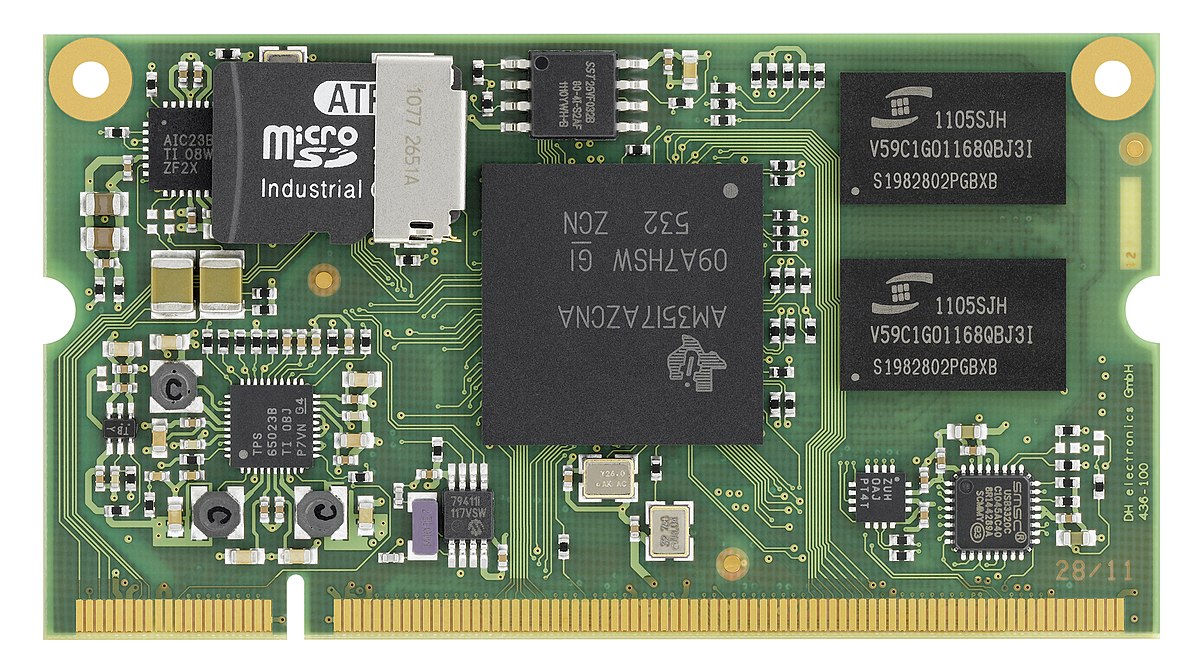

Posted By Michael Crichton Library TEXT ID a4678ea5. Institute of Digital and Computer Systems TKT-9636. A System On A Chip. Low power if application requires portability. Typically uses 70 to 140 mm2 of silicon. Vijayakrishnan Rousseau in System on Chip Interfaces for Low Power Design 2016. Describe all the interfaces between the design and its environment. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involved. System on Chip Interfaces for Low Power Design provides a top-down understanding of interfaces available to SoC developers not only the underlying protocols and architecture of each but also how they interact and the tradeoffs involvedThe book offers a common context to help understand the variety of available interfaces and make sense of technology from different vendors aligned with.

A system includes a microprocessor memory and peripherals. An electronic circuit might consist of a CPU ROM RAM and other glue logic. Low cost Lowest possible area Technology behind the leading edge High level of integration of peripherals reduces system cost Fast time to market Compatible architectures eg. PDF On Sep 9 2015 Jie Jin and others published Low Power Design for On-chip Networking Processing System Find read and cite all the research you need on ResearchGate. Interface to SW register definitions Timing Performance Physical design issues such as area and power. The NCS36510 is a low power fully integrated System on Chip that integrates a 24 GHz IEEE 802154 compliant transceiver Arm CortexM3 microprocessor RAM and FLASH memory a true random number generator and multiple peripherals to support design of a complete and secure wireless network with minimal external components. A SoC is a complete system on a chip.

Post a Comment for "System On Chip Interfaces For Low Power Design Pdf"